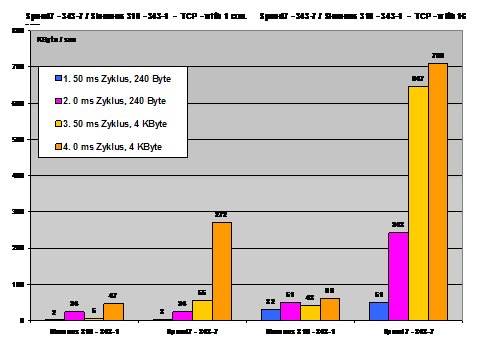

Seit August 2005 steht für die CPUs ein integrierter High-Speed-Ethernet-CP 343 mit RFC1006, TCP/IP und UDP zur Verfügung. Dieser ist mit bis zu 16 Verbindungen projektierbar (je nach CPU-Variante).

Allgemeine Informationen für Speed7

Die CPU mit SPEED7-Technologie ist die erste SPS, die für einen weiten Speicherbereich über eine MCC (Memory Configuration Card) konfigurierbar ist. Natürlich beinhaltet diese neben der Skalierung des Speichers weiterhin die Funktionen der bisherigen VIPA-MMC, beispielsweise als externer Datenspeicher für Sourcen und Programme sowie für Firmware-Updates. Die Standard MMC-Karte kann zum Speichern von Programm und Daten auch dann, wenn die CPU im RUN-Modus ist, genutzt werden. Für den Betrieb der CPUs muss keine Speicherkarte gesteckt werden.

Als integrierte Feldbus-Schnittstelle steht der Profibus zur Verfügung. Weiterhin ist, wie gewohnt, die VIPA MP2I-Schnittstelle mit 12MBaud eingebaut, die außer der Standard-MPI-Kommunikation zum PG auch eine PtP-Verbindung über das VIPA Green Cable erlaubt.

Zusätzlich verfügen die SPEED7-CPUs über eine integrierte Ethernet-Schnittstelle, die dem Anwender eine komfortable Programmierung über Netzwerk erlaubt.

Die Peripherie kann über zwei Arten angeschlossen werden:

1. Wie gewohnt seriell auf der rechten Seite über den S7-300-Standard-Rückwandbus, an dem alle S7-300-I/O-Komponenten sowie auch Kommunikationsprozessoren und Funktionsmodule wie z. B. Zähler zu betreiben sind.

2. Die Besonderheit der CPU 314ST und den 317er CPUs ist der parallele Anschluss über den VIPA Highspeed-Parallelbus auf der linken Seite der CPU, der es dem Anwender ermöglicht, spezielle schnelle Peripheriebaugruppen zu betreiben. VIPA stellt für den Highspeed-Parallelbus FAST digitale Ein-/Ausgänge, FAST analoge Eingänge, FAST Profibus-DP, INTERBUS-Master sowie ein CAN-Interface (siehe Auswahlliste VIPA) zur Verfügung.

VIPA unterstützt mit dem integrierten Master für Profibus-DP, der Ethernet-Schnittstelle und dem MP²I-Anschluss alle wichtigen Interfaces, vereint in einem System.

Technische Daten:

CPUs: Multiprozessorarchitektur, ausgerüstet mit SPEED7-Chip der profichip GmbH

Sprache: STEP7 von Siemens, einstellbar als Typ 300- oder 400-kompatibel

Speicher: CPU 314ST/315SB mit 64kB bis 2MB in Stufen konfigurierbar auf 128, 256 und 512kByte, 50% Programm und 50% Daten oder CPU 317NET mit 512kByte in Stufen konfigurierbar auf 1, 2, 4 und 8 MByte, 50% Programm und 50% Daten, kein Ladespeicher erforderlich

Peripherieinterface: Doppelbusarchitektur

1. serieller Bus kompatibel zur S7-300 von Siemens mit bis zu

32 Modulen pro Reihe

2. VIPA CPU 314ST/317Sx Highspeed-Parallelbus, 32Bit,

16 Steckplätze (Slot) je 64kByte Adressraum. In Gruppen zu je

4 Port ausbaubar; Datentransferrate > 40 MByte pro Sekunde,

interruptfähig

Zeiten:

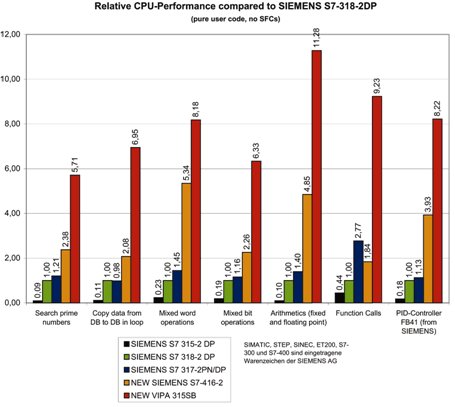

Befehle: Bit-Operationen, ab 15ns

Wort-Operationen, ab 15ns

Festpunktarithmetik, ab 15ns

Gleitpunktoperationen, ab 86ns

Zyklus: Standardzyklus ab 100µs (Leerlauf) Anwenderprogramm-

Laufzeit: 100k Anweisungen im Befehle-Mix typ. 2,1ms

Zyklusmodi einstellbar

1. Klassischer LBS-Modus (lesen, bearbeiten, schreiben), Default

2. Fast-Parallel-Modus, B+SL-Mode (bearbeiten, schreiben + lesen)

interrupt: Prozessalarmreaktionszeit ab 100µs

Weckalarm: Highspeed Weckalarm OB 29 für 500µs, OB 28 für 250µs! Laufzeit OBs + Weckalarm sollten ? 50% Gesamtperformance

sein

Interfaces Basis CPU

Schnittstelle 1: MP²I-Interface, MPI für 32 Verbindungen, 12MBaud und PtP 3964R, DSub-9

Schnittstelle 2: Profibus-DP-Master für bis zu 126 Slaves, DSub-9

Schnittstelle 3: Ethernet-Slot für PG-Kommunikation RJ45

Schnittstelle 4: USB 2,0 Interface zur Einkopplung in das MPI-Netzwerk, Stecker A (CPU317) NET-CPU 317SN/NET

Schnittstelle 5: Ethernet CP 343, RJ45