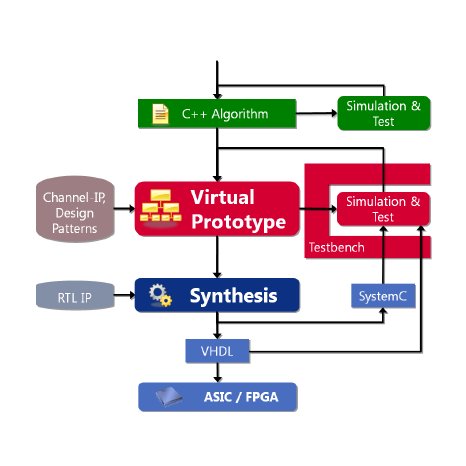

In the tutorial, CoSynth will summarize the major advantages of high level design processes and present the general steps of such a process based on an example design. The most crucial component of this process is the synthesis tool. It automates the conversion from high-level descriptions to hardware designs. The CoSynth Synthesizer provides an automatic conversion from designs written in C++ and SystemC to VHDL, mainly targeting FPGA-based platforms. Another important aspect is the integration of the synthesis results into a complete system design. This is also covered in detail in the tutorial.

The tutorial is based on the running example of a hardware accelerated video filter chain. The requirements and development steps for system level design are discussed. The whole design process, from an initial C++ implementation to the final IP core, is shown. A special focus is put on the refinement of the SystemC virtual platform into a synthesizable representation. This code is then transformed into VHDL utilizing the CoSynth Synthesizer tool. The necessary coding guidelines and typical restructuring measures of the code are detailed in several examples. The synthesis result is combined into an existing FPGA-based system with camera and display interfaces. Using the Xilinx EDK, the synthesized IP core and the base platform are integrated into a running design for Xilinx FPGAs.

CoSynth offers a wide range of tutorials and workshops on System Level Design and Synthesis. Further details, also about the CoSynth Synthesizer tool, are available upon request.