Startseite unserer Website: http://www.electronicprint.eu/...

Der Trend bei der Entwicklung neuster elektronischer Baugruppen ist ein deutlicher Anstieg der Dichte bis zu unter 4 mil. Der Trend zu kleineren Bauelementen hat zur Folge das die Packungs- dichte bei den Leiterplatten zunimmt.

Durch die Verringerung von Leiterbahnbreiten und Abständen sowie den Einsatz von Blind Vias (Sacklöcher) und Buried Vias bei Multilayern kann die Packungsdichte erhöht werden und somit bei kleinerer Größe der Leiterplatte mehr Funktion erziehlt werden.

Mit dem Einsatz von Buried Vias können Bohrungen über alle Lagen der Leiterplatte vermieden werden, somit entstehen auf den Außenlagen zusätzliche Bestückungsflächen.

Begriffsklärungen

HDI oder auch High Density Interconnection genannt

Ist eine Leiterplatte mit Microvias und feinsten Strukturen. Sequentieller Multilayeraufbau mit mindestens 2 Pressvorgängen

Buried Via auch Vergrabenes Via genannt

Ist eine im Kern liegende und außen nicht sichtbare Durchkontaktierung

Blind Via (Sackloch)

Ist eine auf einer Innenlage endende Ankontaktierung

Microvia

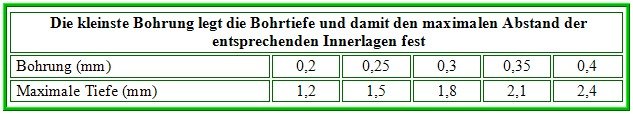

An/Durchkontaktierung mit ø <0,20mm

1. Durchkontaktierungen bei mehrlagigen-Leiterplatten

2. Die Durchkontaktierungen verbinden stets alle Ebenen eines Multilayers (Montagebohrung, Bauteilbohrung, Durchkontaktierung )

Siehe: http://www.electronicprint.eu/...

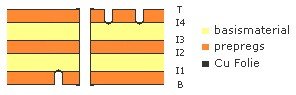

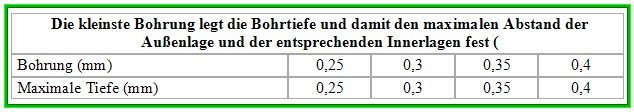

1. Blind vias bei Multilayer-Leiterplatten

2. Blind Vias verbinden immer eine Außenlage mit einer oder mehreren Innerlagen

Siehe: http://www.electronicprint.eu/...

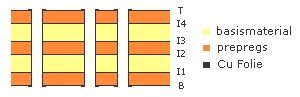

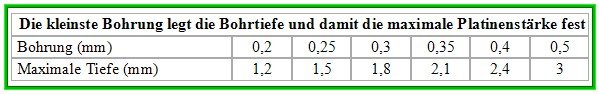

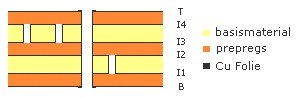

1. Buried vias bei Multilayer-Leiterplatten

2. Buried Vias verbinden mindestens zwei Innerlagen eines Multilayers. Sie haben niemals Kontakt zu den Außenlagen einer Leiterplatte

Siehe: http://www.electronicprint.eu/...

Qualitätssicherung bei hoher Packungsdichte der Leiterplatte

Für eine qualitativ hochwertige Fertigung werden die Fertigungsschritte zwischendurch mit Schliffuntersuchungen überwacht.

* Cu-Schichtdicke in den Buried Vias >15µm

* Dickengenauigkeit und Verteilung nach den Pressvorgängen

* Registrierung der Blind Vias auf den Innenlagen bei Leiterplatten

* Anbindungszuverlässigkeit bei der Bohrtiefe der Blind Vias (15µm)

* Cu-Schichtdicke in den Blind Vias >20µm